Paper Sharing: Abnormal Voltage Compensation Caused by Vertical Crossing in Phase-Shifted PWM-Based Cascaded H-bridge Inverters

We are pleased to introduce the paper “Abnormal Voltage Compensation caused by Vertical Crossing in Phase-shifted PWM-based Cascaded H-bridge Inverters” written by Jeong-Yul Bang, Dongho Choi, Hyeon-Woo Oh, June-Seok Lee from Dankook University.

The paper was presented at 2024 IEEE Energy Conversion Congress and Exposition (ECCE).

Know more about this paper:

https://ieeexplore.ieee.org/abstract/document/10861276

Brief introduction:

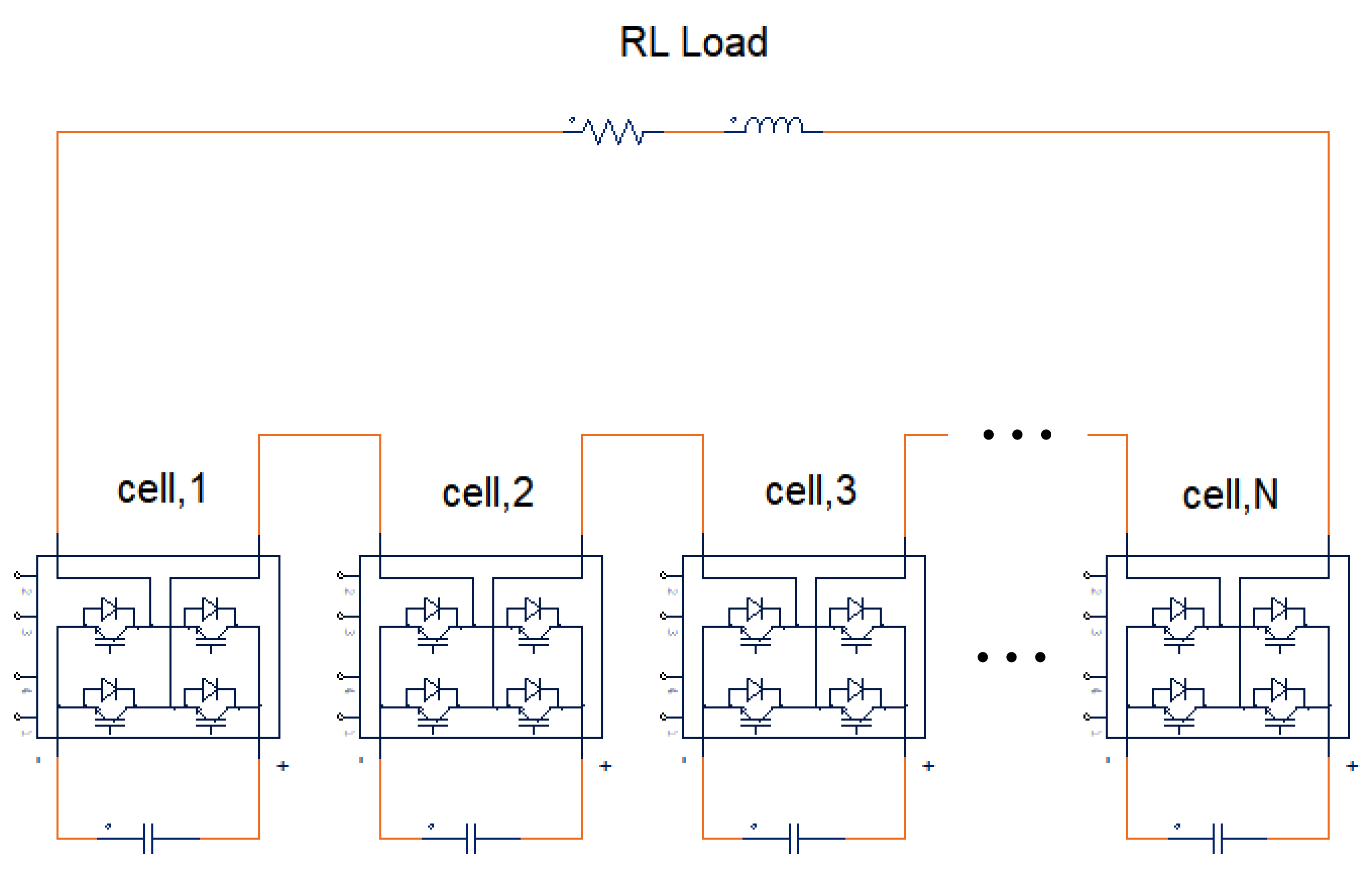

The paper presents a compensation method for abnormal voltage generation in phase-shifted PWM-based cascaded H-bridge inverters caused by vertical crossing. Vertical crossing, which leads to missed PWM pulse updates and subsequent voltage errors and current surges, is predicted by analyzing the modulation wave and carrier slope at every sampling instance. The proposed approach adjusts the modulation wave in the affected inverter cell to suppress vertical crossing and compensates for the resulting voltage error by redistributing it to the other cells. DSIM simulation results validate the effectiveness of this method, demonstrating its capability to maintain accurate output voltage and mitigate current surges in cascaded H-bridge inverter systems.

Cascaded H-bridge inverter vertical crossing suppression simulation using DSIM

To investigate the effects of vertical crossing on the output voltage and load current in phase-shifted PWM-controlled cascaded H-bridge inverters, DSIM is used to simulate a three-cell cascaded H-bridge inverter equipped with a multi-sampling control strategy (three samples per carrier period). The analysis focuses on the suppression effects of the compensation algorithm on voltage errors (e.g., Em) and current surges (e.g., iLoad spikes). By comparing waveforms before and after compensation (such as vcell,x, vCHB, and iLoad), the simulation verifies the effectiveness of the proposed method in eliminating vertical crossing issues. Additionally, a systematic validation is conducted using an RL load (20 Ω/1.9 mH) and a specific carrier frequency (1.67 kHz), with one real-life hour represented as one simulated second.